Xilinx Vivado Download Design Suit Crack

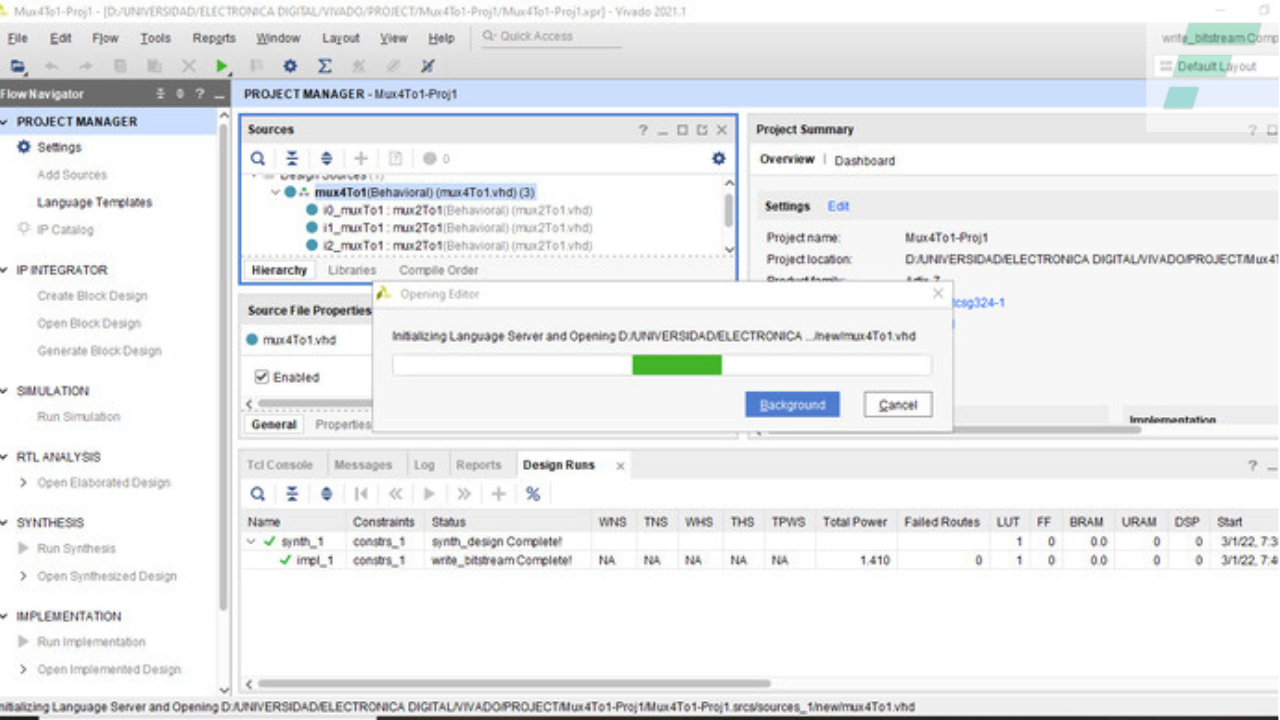

Xilinx Vivado Download is an integrated development environment (IDE) that enables engineers and designers to develop FPGA and SoC-based applications. It offers a range of tools and features essential for the entire development lifecycle, including design entry, synthesis, implementation, and verification. Vivado supports a variety of languages for design entry, including VHDL, Verilog, and SystemVerilog, making it a flexible choice for designers.

The primary purpose of Xilinx Vivado is to facilitate the design and implementation of FPGA and SoC-based systems. It streamlines the design process, allowing developers to efficiently create, optimize, and validate their designs. Vivado provides a platform for integrating hardware and software components, ultimately accelerating the time-to-market for electronic products.

With Vivado, designers can optimize their designs for performance, power, and resource utilization, ensuring that their FPGA-based applications meet specific requirements. The software offers powerful analysis and debugging tools, aiding in the identification and resolution of design issues. This comprehensive toolset makes Vivado an indispensable solution for FPGA and SoC development.

Xilinx Vivado Download Latest Version

Download Link

Key Features

- Design Automation and Optimization: Vivado provides automated design and optimization capabilities, enhancing productivity and ensuring optimal resource utilization within FPGA architectures.

- Hierarchical Design Approach: The software allows designers to manage complex projects through a hierarchical design methodology, promoting modularity and reusability.

- Integrated IP Integrator: Vivado includes an IP integrator that simplifies the integration of predefined intellectual property (IP) blocks into the design, reducing development time.

- High-Level Synthesis (HLS): Vivado supports HLS, allowing designers to write their algorithms in high-level languages like C/C++ and convert them into optimized hardware implementations.

- Advanced Verification and Debugging Tools: The toolset includes advanced simulation, debugging, and verification features to help identify and resolve design issues quickly and efficiently.

- Multi-Language Support: Vivado supports multiple design entry languages, including VHDL, Verilog, and SystemVerilog, providing flexibility and accommodating diverse design styles.

- Partial Reconfiguration Support: This feature enables specific regions of the FPGA to be reconfigured while the rest of the design remains operational, allowing for dynamic updates and system enhancements.

- Cross-Correlation of Hardware and Software Development: Vivado facilitates the seamless integration of hardware and software components, enabling concurrent development and verification of both aspects of the system.

- Power Analysis and Optimization: The software offers tools to analyze and optimize power consumption within the FPGA design, critical for power-sensitive applications.

What’s New?

The latest version of Xilinx Vivado brings several new features and enhancements to further streamline the FPGA and SoC development process:

- Enhanced HLS Performance: The new version provides improved performance and efficiency for high-level synthesis, allowing for faster design iterations and optimized implementations.

- Intelligent Design Automation: Vivado now incorporates AI-driven design automation, enhancing productivity and efficiency in design flows.

- Expanded IP Library: The updated version includes an expanded IP library with additional pre-designed IP blocks, reducing design time and effort.

- Enhanced Power Optimization: The latest Vivado release includes advanced features for better power optimization, crucial for energy-efficient designs.

- Improved Debugging Tools: The debugging tools in Vivado have been enhanced for better visibility into the design and faster identification of issues.

System Requirements

To run Xilinx Vivado, your system needs to meet the following minimum requirements:

- Operating System:

- Windows 10 (64-bit)

- Linux: Red Hat Enterprise Linux 7.4 or later (64-bit)

- CentOS 7.4 or later (64-bit)

- Ubuntu Linux 18.04 LTS (64-bit)

- Processor:

- Intel Core i5 or equivalent (minimum)

- Intel Core i7 or equivalent (recommended)

- RAM:

- 16 GB (minimum)

- 32 GB or more (recommended)

- Hard Drive Space:

- 200 GB of free disk space (minimum)

- SSD with high read/write speed (recommended)

- Graphics:

- 1024 x 768 resolution (minimum)

- 1920 x 1080 resolution or higher (recommended)

How to Install

Installing Xilinx Vivado is a straightforward process. Follow these steps:

- Download Vivado: Go to the official Xilinx website and download the Vivado installer appropriate for your operating system.

- Run the Installer: Double-click the downloaded installer to launch the installation process.

- Follow Installation Wizard: The Vivado Installation Wizard will guide you through the installation process. Follow the on-screen instructions, including selecting the desired installation location and options.

- Complete Installation: Once the installation is complete, you can launch Vivado and start using it for your FPGA and SoC development projects.

Conclusion

Xilinx Vivado Download stands as a comprehensive and powerful software suite for FPGA and SoC development. With its wide range of features and capabilities, it simplifies and accelerates the design process, from conception to implementation. Its advanced design automation, IP integration, and optimization capabilities make it an indispensable tool for engineers and designers working in the field of digital system development. Keeping up with the updates and ensuring your system meets the necessary requirements will ensure a smooth and efficient experience with Vivado, ultimately aiding in the successful realization of your FPGA and SoC-based projects.